| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

- SQL

- MYSQL

- Brute Force

- binary search

- two pointer

- String

- union find

- 그래프

- 다익스트라

- Dijkstra

- Two Points

- DP

- Stored Procedure

- 스토어드 프로시저

- 이진탐색

- Hash

- Trie

- Today

- Total

codingfarm

4. 컴퓨터 구조에 대한 두 번째 이야기 본문

1. 컴퓨터 구조의 접근방법

컴퓨터 디자인

$\bullet$ CPU의 Register 만을 디자인 대상으로 삼는다.

(ALU와 Control Unit은 이미 있다고 가정한다.)

$\bullet$ 시스템 프로그래머 입장에서 CPU를 보는 관점은 Register에 집중된다.

여기서 시스템 프로그래머란 CPU에 종속적인 어셈블리 프로그래밍을 하는 개발자이다.

레지스터 디자인

ARM 코어를 참조하여 레지스터를 디자인 해보자.

| r0 | |

| r1 | |

| r2 | |

| r3 | |

| r4 | ir |

| r5 | sp |

| r6 | lr |

| r7 | pc |

ir(instruction register), sp(stack pointer), lr(link register), pc(program counter)

명령어 구조 및 명령어 디자인

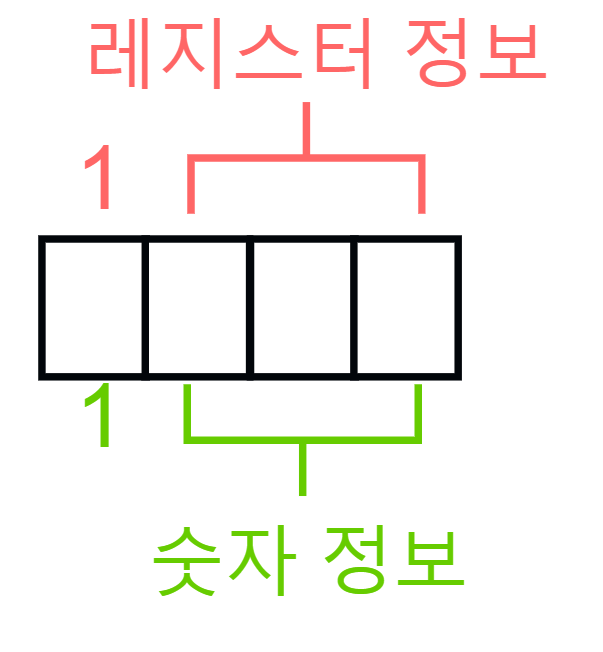

$\bullet$ 레지스터의 디자인을 바탕으로 명령어로 디자인 시킨다.

$\bullet$ CPU가 달라지면 명령어 구조도 달라진다.

(어셈블리 언어로 구현된 프로그램은 다른 CPU로 이식이 불가능하다.)

1) 16bit 명령어 디자인

$\bullet$ 16bit 안에 최대한 많은 정보를 넣어야 한다.

ex) 레지스터 r1에 있는 값과 7을 더하여 레지스터 r2에 저장시켜라

$\bullet$ 저장소 : 레지스터가 총 8개 이므로 3bit로 충분($2^3 = 8$)

$\bullet$ 연산자 : 사칙연산의 기능을 담당한다.

| 덧셈의 의미 | 심볼 | 2진 코드 |

| 덧셈 | ADD | 001 |

| 뺄셈 | SUB | 010 |

| 곱셈 | MUL | 011 |

| 눗셈 | DIV | 100 |

$\bullet$ 레지스터의 심볼

| 레지스터 심볼 | 2진 코드 |

| r0 | 000 |

| r1 | 001 |

| r2 | 010 |

| r3 | 011 |

| r4( ir) | 100 |

| r5 (sp) | 101 |

| r6 (lr) | 110 |

| r7 (pc) | 111 |

즉 위의 예는 아래와 같이 정의된ㄷ:

어셈블리 언어 : ADD r2, r1, 7

바이너리 코드 : 00/001/010/1001/0111

ir(Instruction Register) : 다음번에 실행될 명령어를 미리 가져다 놓는 용도의 register

RISC와 CISC

CISC(Complex Instruction Set Computer)

$\bullet$ 제약사항을 없에기 위해 만든 CPU이다.

$\bullet$ 명령어의 수가 매우 많고 그 조합도 다양하다.

$\bullet$ 자주 쓰는 명령어가 전체의 10%가 안된다.

$\bullet$ CPU구조가 복잡하고, 명령어의 크기도 일정치 않다.

RISC(Reduced Instruction Set Computer)

$\bullet$ 명령어의 수가 CISC의 10% 수준이다.

$\bullet$ 명령어의 크기가 일정하다.

$\bullet$ 초당클럭수가 높으며 클럭당 처리할 수 있는 명령어의 개수가 2개 이상이다.

$\bullet$ 명령어 길이가 동일하고 명령어를 처리하는 과정이 일정하다.

요약

1. 명령어

2. CPU의 내부 연산과 레지스터

3. Direct vs Indirect

'Windows > 윈도우즈 시스템 프로그래밍' 카테고리의 다른 글

| 7. 프로세스간 통신(IPC) 1 (0) | 2021.05.14 |

|---|---|

| 6. 커널 오브젝트와 오브젝트 핸들 (0) | 2020.06.15 |

| 5. 프로세스의 생성과 소멸 (0) | 2020.06.15 |

| 2. 아스키코드와 유니코드 (0) | 2020.05.29 |

| 1. 컴퓨터 구조에 대한 첫 번째 이야기 (0) | 2020.05.29 |